ModelSim是Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,因为业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器,它提供最友好的调试环境,是唯一的单内核支持VHDL和Verilog混合仿真的仿真器。是唯一一款将单核模拟技术与VHDL和Verilog统一调节环境相结合的软件,是作FPGA/ASIC设计的RTL级和门级电路仿真的首选,它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段。欢迎有需要使用这款Modelsim se 10.1a的用户前来WinWin7分享的地址获取!

破解教程

本破解还是根据之前网络上流传的其他版本摸索着破解的,在我的电脑上modelsim 10.1a win7 32,

已经经过验证成功,其他系统和版本应该也可以的,需要的自行尝试。

将MentorKG.exe和crack.bat文件复制到安装根目录win32目录下,运行crack.bat文件,生成txt文件后另存,将另存的路径添加为系统环境变量LM_LICENSE_FILE

如D:\modeltech_10.1a\LICENSE.TST

OK ! 破解成功!

安装方法

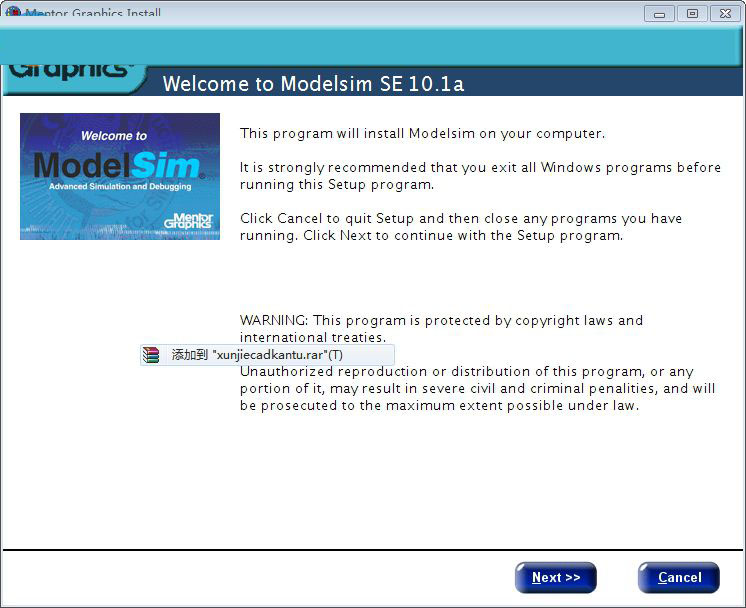

1、下载文件找到"modelsim-win32-10.1a-se.exe"双击运行,进入软件安装向导界面;

2、进入软件的安装向导界面,点击Next进行安装,见下图所示:

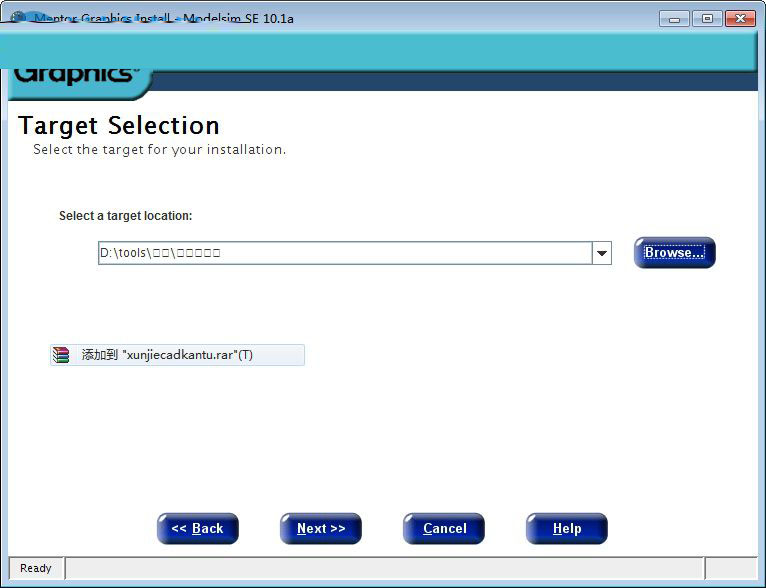

3、选择软件安装的位置,默认位置“C:\modeltech_10.1a”,建议安装在D盘,点击Next,见下图所示:

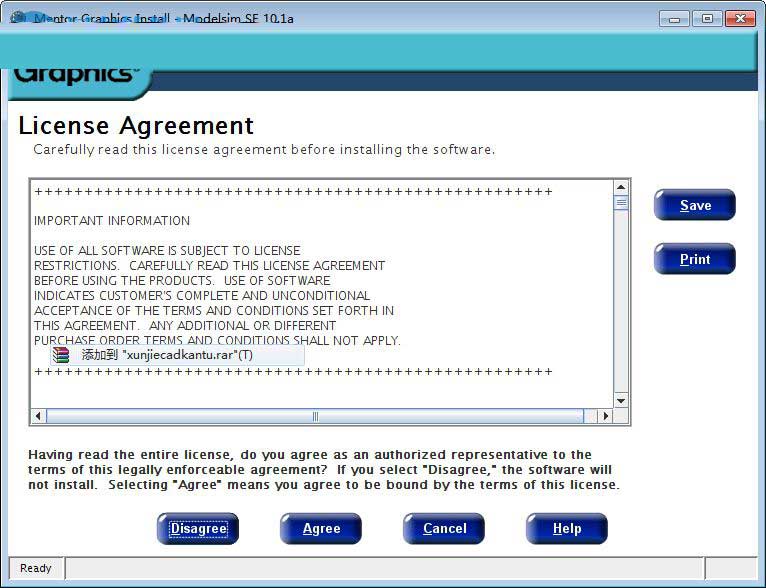

4、点击Agree我同意软件的许可协议,见下图所示:

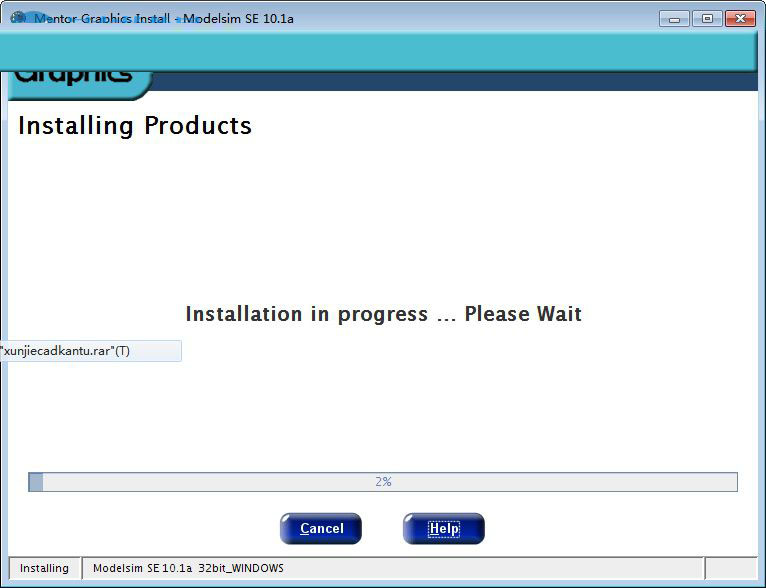

5、modelsim 10.1a破解版正在进行快速的安装,请耐心等待.....,见下图所示:

6、modelsim 10.1a破解版已经安装能完成,点击Finish;

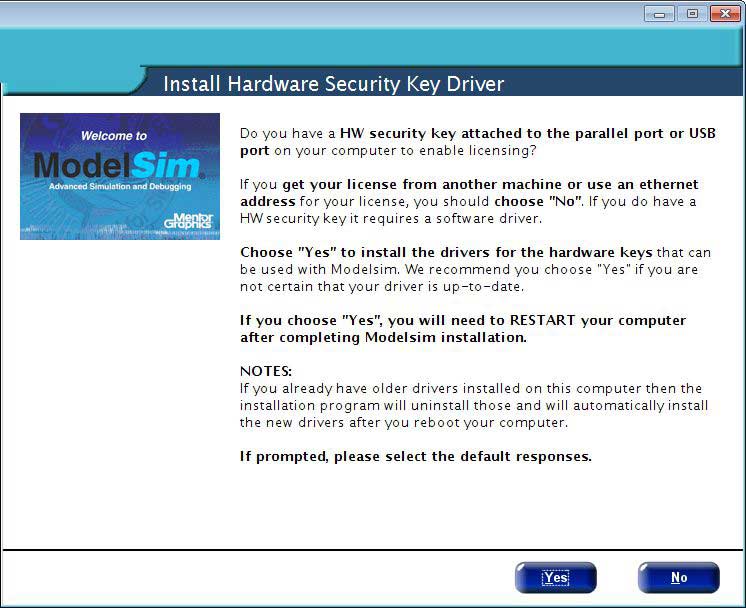

7、点击YES即可启动软件;,见下图所示:

使用教程

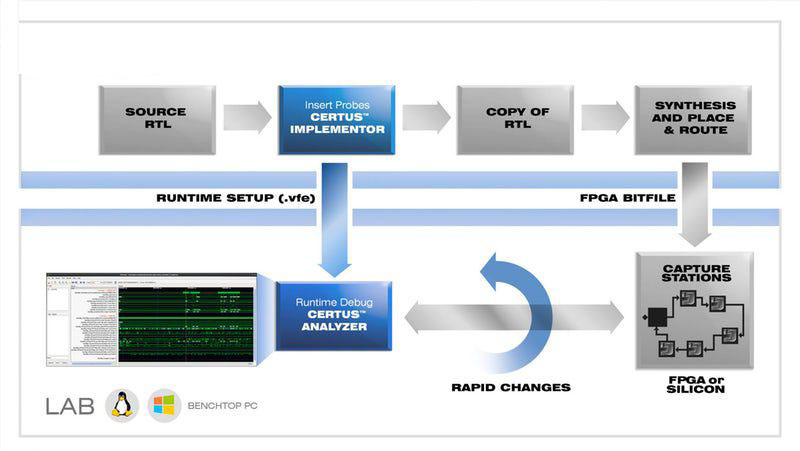

Mentor调试解决方案最大限度地提高了完整SoC设计和验证周期的性能,容量和自动化。与Questa Simulation和Veloce Emulation紧密集成,该解决方案包括业界领先的Codelink硬件和软件调试产品系列,以及用于测试平台和硬件调试的新型Visualizer调试环境,见下图所示:

通过实现高达数万个信号的测量,实现了调试系统和芯片级问题,能够捕获非常深的痕迹。无论您的目标FPGA实施流程如何,轻松的软件驱动,运行时可配置性都可以消除昂贵的重新测试自旋,见下图所示:

最新一代数字录像(DVR)设备的工作方式相同。在功能仿真或仿真过程中,Codelink的高级跟踪技术可自动捕获并压缩设计处理器内的所有重要活动。验证工程师可以通过快进,快退,重放,暂停,慢动作,放大,单步和平移等功能“回放”模拟或仿真运行,见下图所示:

一切都完全同步,易于查看,包括逻辑仿真波形,处理器状态,源代码,内部存储器,寄存器,堆栈和输出。Codelink然后仅提供快速调试软件驱动测试所需的重要信息。

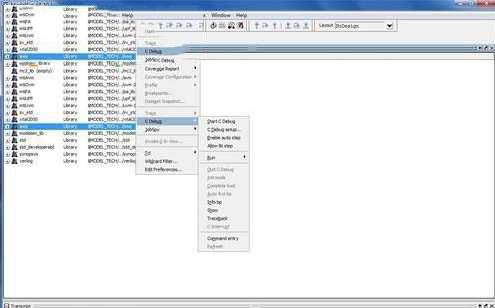

公司已经能够将系统级的调试从几个月减少到几天。现在可以在单个多视图调试环境中诊断复杂故障。这种故障需要对多个文件和数据库进行广泛的分析,见下图所示:

Modelsim功能

ModelSim有几种不同的版本:SE、PE、LE和OEM,其中SE是最高级的版本,而集成在 Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本。

SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE 比ModelSim XE要快10倍;对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。

有se、de、pe等多个版本,对应Altera和Xilinx还有对应的OEM版本,所有的版本功能最强速度最快的就是se,反正也是要破解,自然就装最强的版本了,和Altera网站上的modelsim的区别在于,se的版本我们需要自己编译对应的库,所以Altera和Xilinx的都是自带对应的库无需编译的,像我这样同时装了Quartus II和ISE的,自然还是自己编译方便一点。

Modelsim特色

统一的混和语言表达仿真模拟模块,易于应用和特性

适用Verilog,SystemVerilog开展设计方案,VHDL和SystemC,以合理地认证繁杂的设计自然环境

迅速调试,易于应用,多语言表达调试自然环境

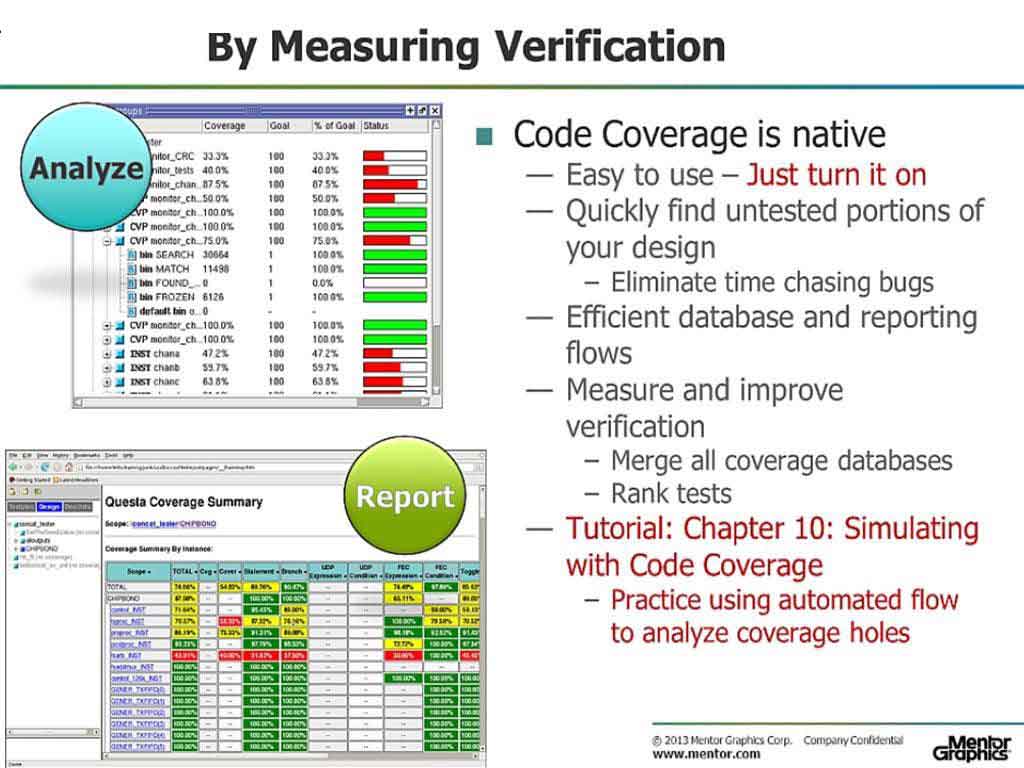

高端编码覆盖和分析工具,可迅速覆盖封闭式

我nteractive和Post-SIM卡调试用以2个可以用,因而同样的调试自然环境

强劲的波形图较为便捷剖析差别和不正确

统一覆盖数据库查询,具备完善的互动式和HTML汇报和处置作用,可以在所有工程中知晓和调试覆盖范畴

再加上HDLDesigner和HDL做为详细的设计写作,项目风险管理和数据可视化作用的创作者

句子覆盖:运作期内实行的句子数

分支覆盖:危害HDL实行控制流的表达式和case语句

标准覆盖:将分支上的条件转化成使结论为真或假的原素

表达覆盖:与标准覆盖同样,但包含并行处理数据信号分派而不是分支确定

关键表达覆盖:以明确覆盖结论中表达式的每一个单独键入的形式展现表达覆盖数据信息

提高的转换覆盖:在默认设置方式下,记数从低于高和从高到低的变换;在拓展方式下,记数到X的变换

有有限状态机覆盖:国家和国家衔接覆盖

上一篇:OpenCV计算机视觉库

360解压缩软件2023

360解压缩软件2023 看图王2345下载|2345看图王电脑版 v10.9官方免费版

看图王2345下载|2345看图王电脑版 v10.9官方免费版 WPS Office 2019免费办公软件

WPS Office 2019免费办公软件 QQ浏览器2023 v11.5绿色版精简版(去广告纯净版)

QQ浏览器2023 v11.5绿色版精简版(去广告纯净版) 下载酷我音乐盒2023

下载酷我音乐盒2023 酷狗音乐播放器|酷狗音乐下载安装 V2023官方版

酷狗音乐播放器|酷狗音乐下载安装 V2023官方版 360驱动大师离线版|360驱动大师网卡版官方下载 v2023

360驱动大师离线版|360驱动大师网卡版官方下载 v2023 【360极速浏览器】 360浏览器极速版(360急速浏览器) V2023正式版

【360极速浏览器】 360浏览器极速版(360急速浏览器) V2023正式版 【360浏览器】360安全浏览器下载 官方免费版2023 v14.1.1012.0

【360浏览器】360安全浏览器下载 官方免费版2023 v14.1.1012.0 【优酷下载】优酷播放器_优酷客户端 2019官方最新版

【优酷下载】优酷播放器_优酷客户端 2019官方最新版 腾讯视频播放器2023官方版

腾讯视频播放器2023官方版 【下载爱奇艺播放器】爱奇艺视频播放器电脑版 2022官方版

【下载爱奇艺播放器】爱奇艺视频播放器电脑版 2022官方版 2345加速浏览器(安全版) V10.27.0官方最新版

2345加速浏览器(安全版) V10.27.0官方最新版 【QQ电脑管家】腾讯电脑管家官方最新版 2024

【QQ电脑管家】腾讯电脑管家官方最新版 2024 360安全卫士下载【360卫士官方最新版】2023_v14.0

360安全卫士下载【360卫士官方最新版】2023_v14.0